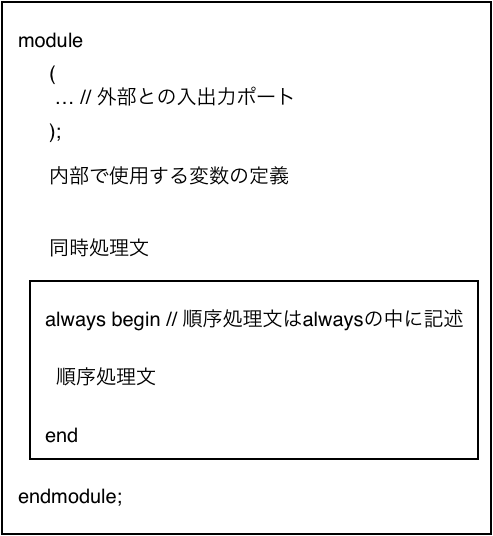

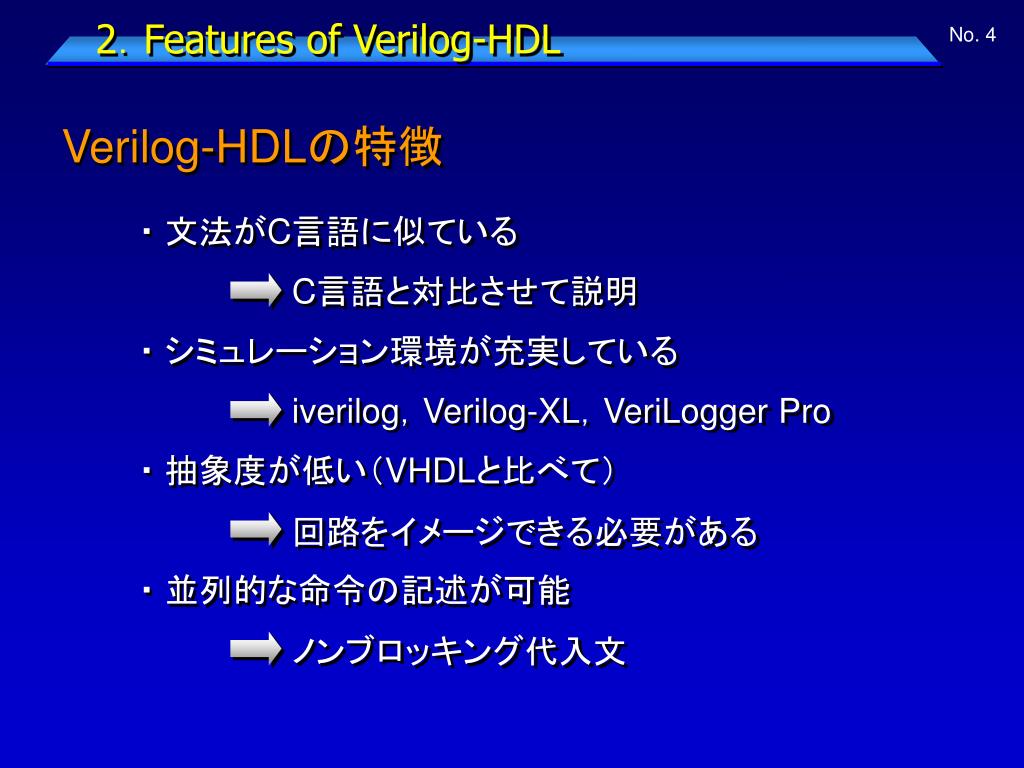

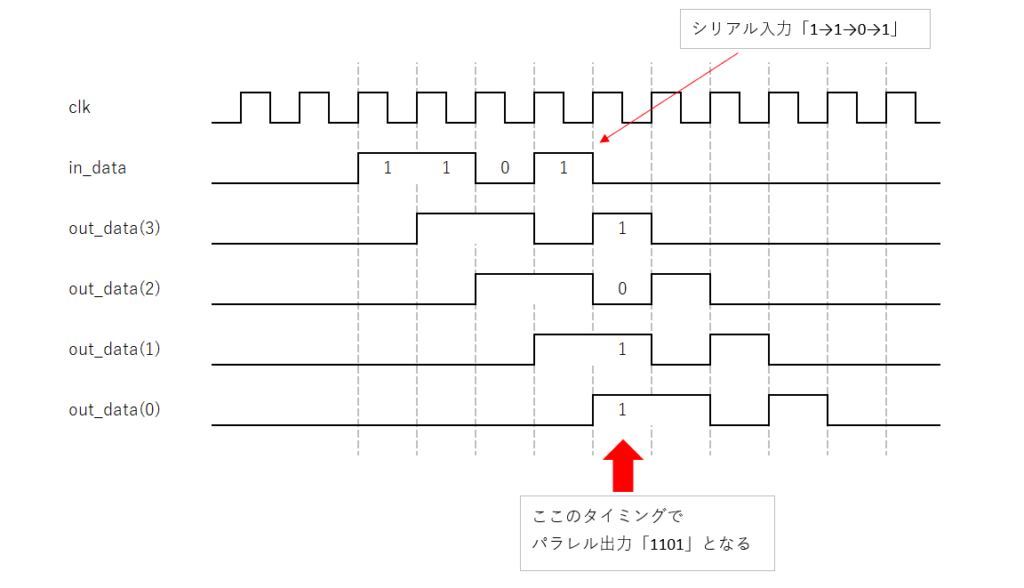

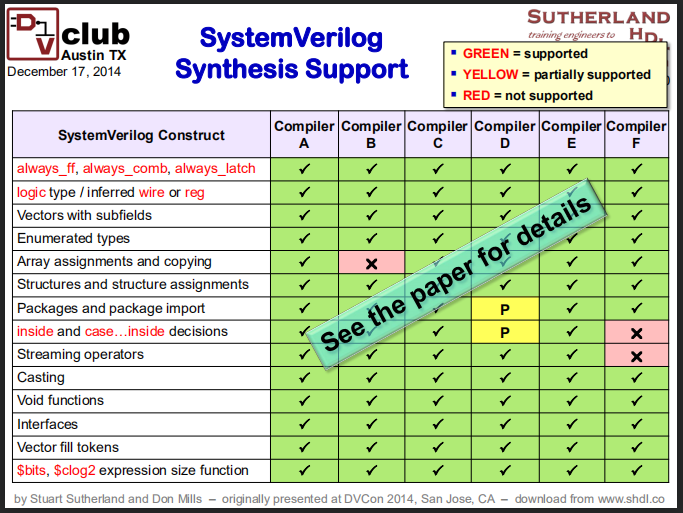

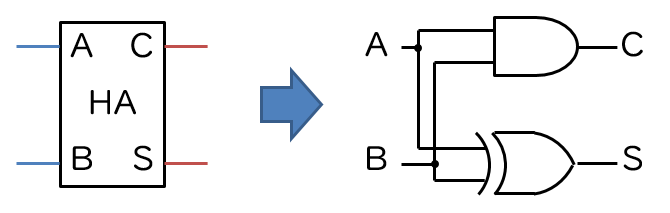

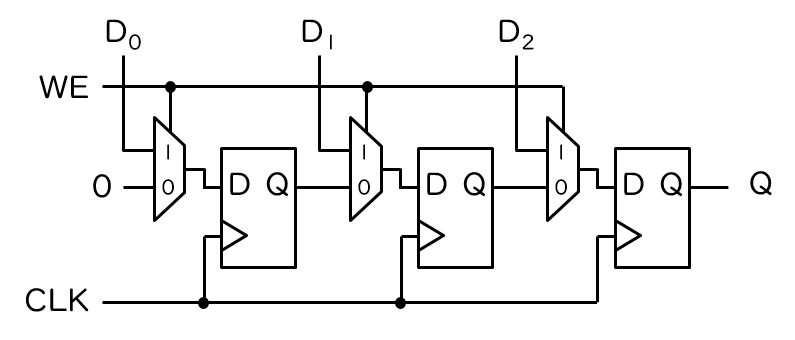

SystemVerilogのサンプルコード集です 目次 Dフリップフロップ Dフリップフロップ (Enable付き) カウンタ クリップ 加算後クリップ 減算後クリップ 乗算回路

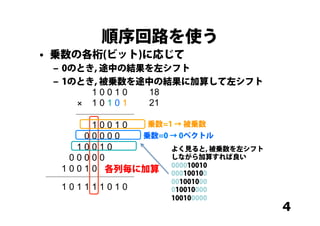

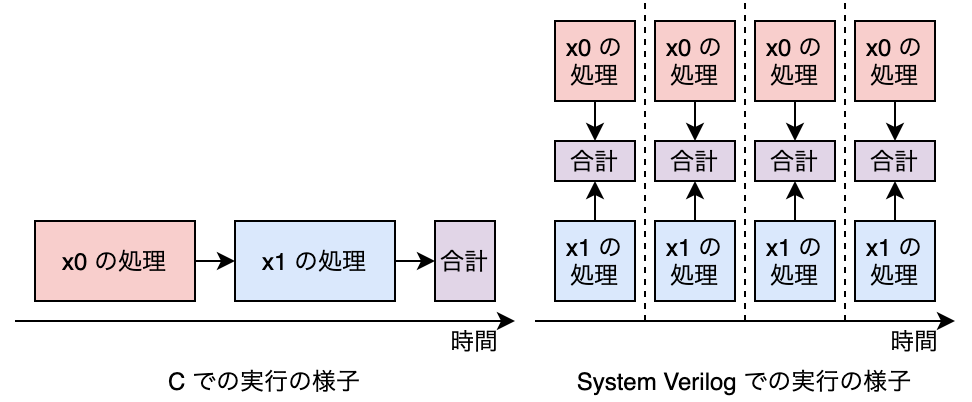

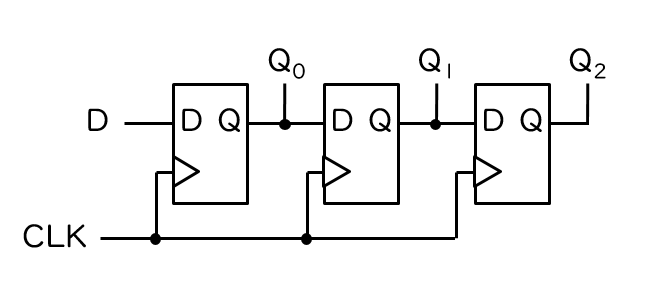

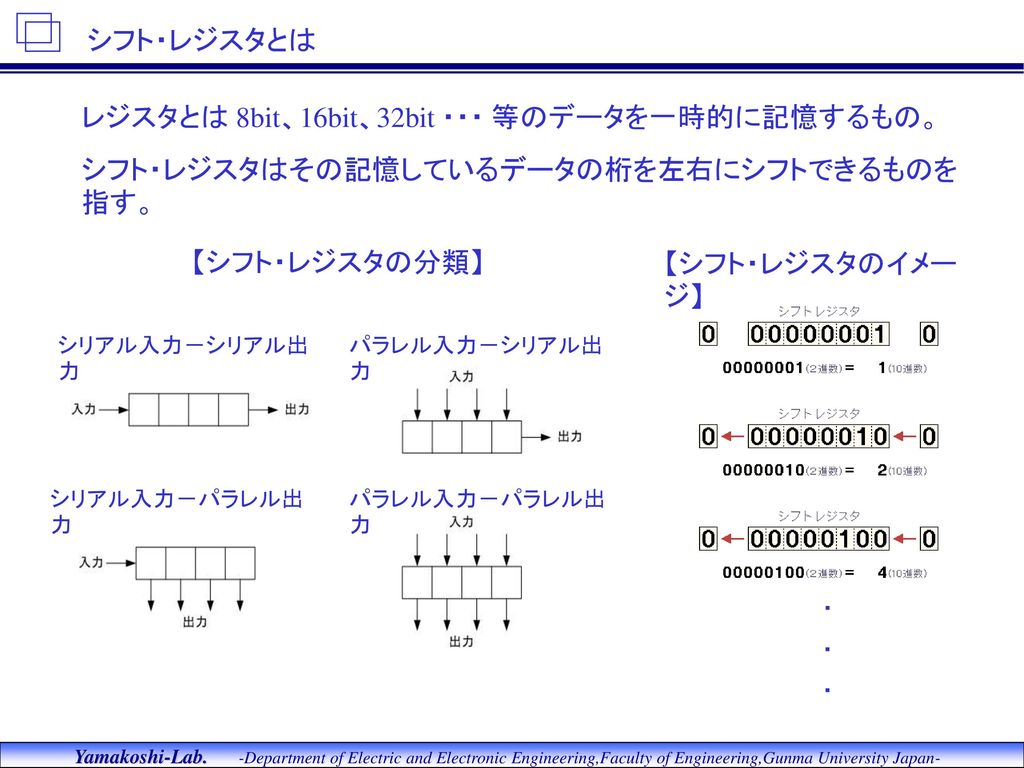

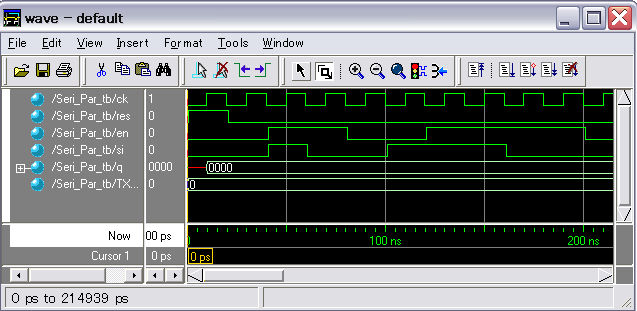

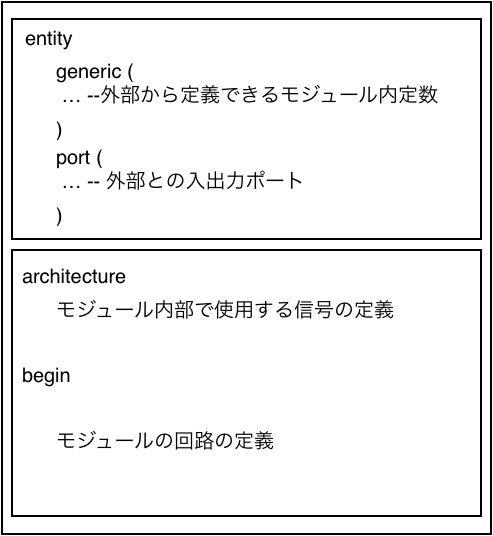

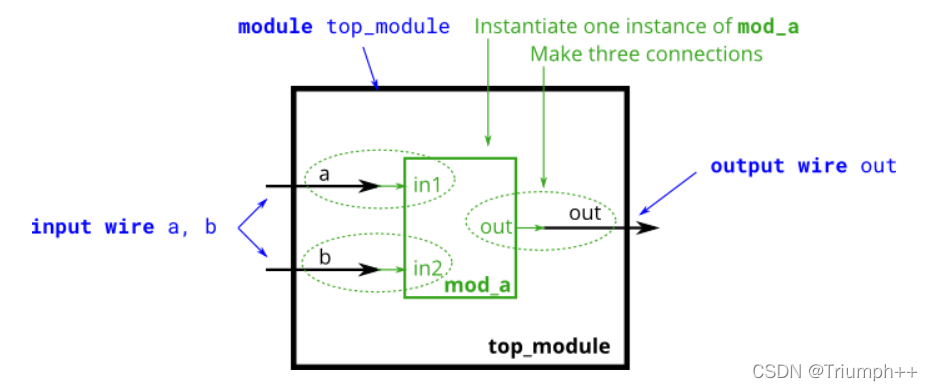

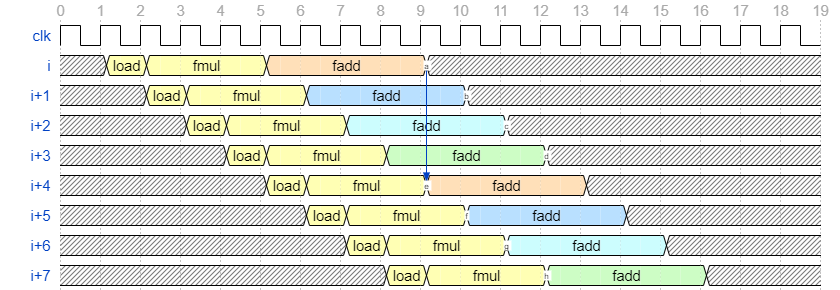

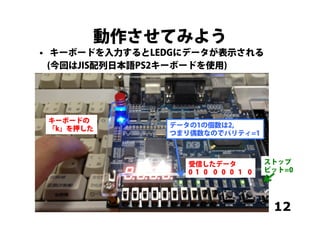

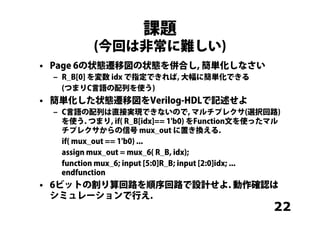

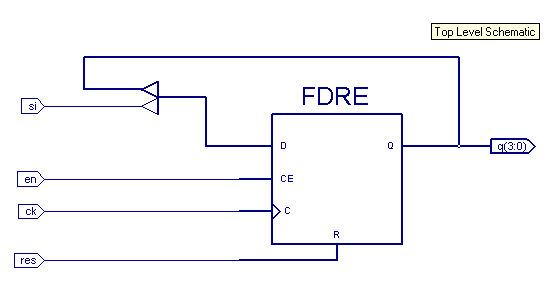

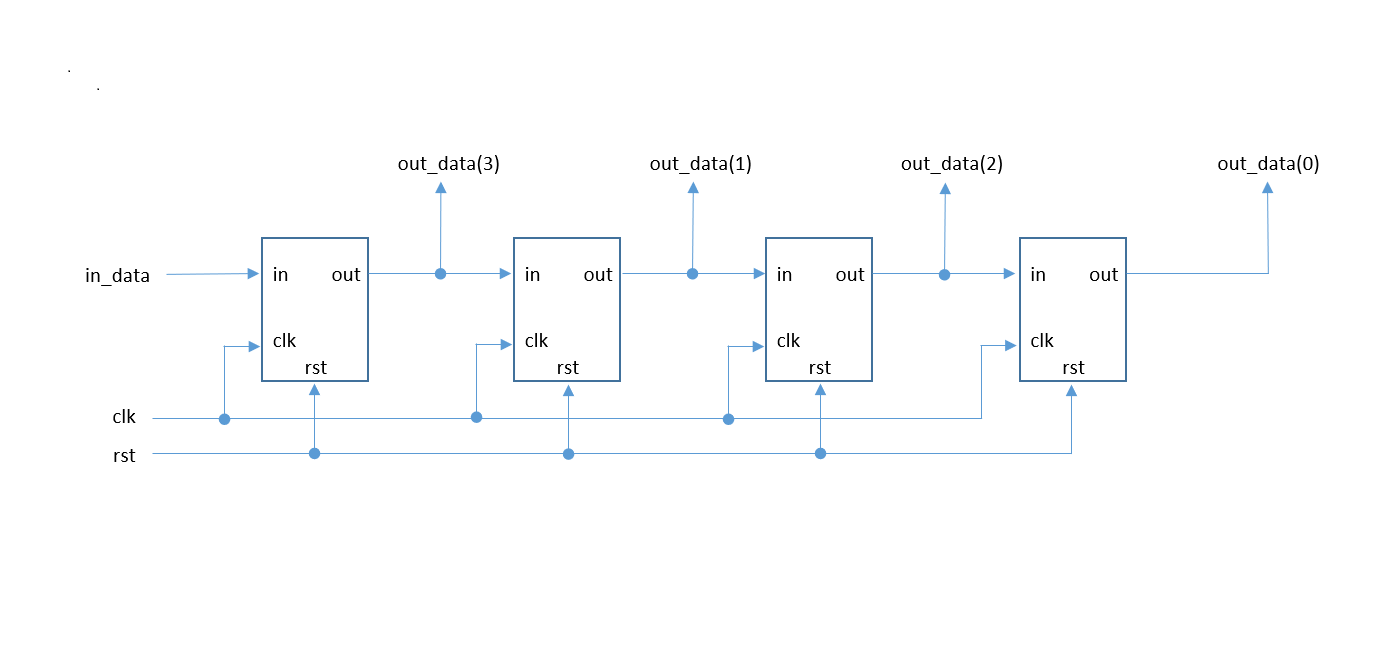

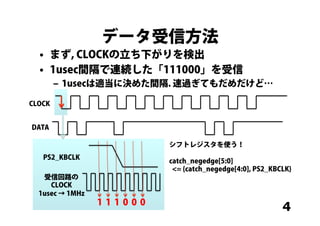

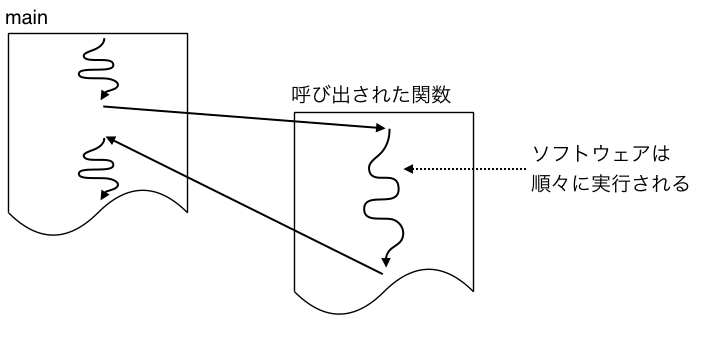

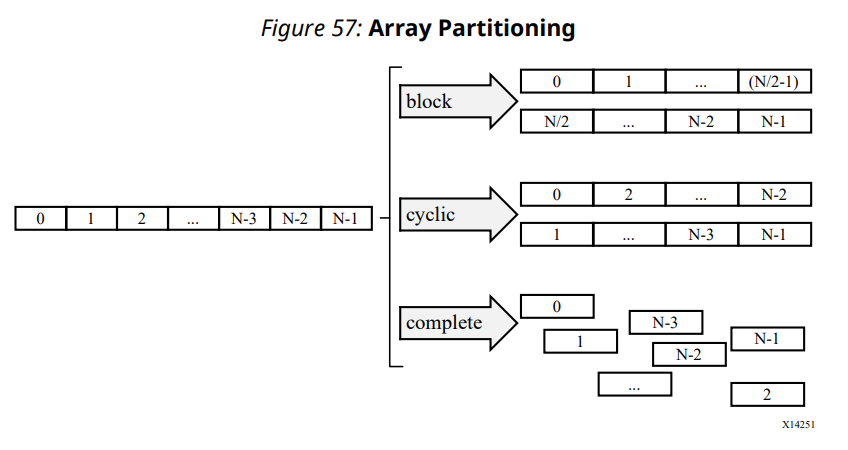

Verilog シフトレジスタ 配列-VerilogHDLは1次元配列しかサポートしませんが、SystemVerilogは、多次元配列をサポートします。 配列へのアクセスが容易になり記述量が減ります。 logic mem 255 0 ;レジスタのリセットは非同期にする シフト演算 ないと困るし,数値にしていると変更するときむっちゃ面倒くさいことになる.そこで,verilogでもparameterを使って同じことができる.これを使えば,module呼び出しとかでも役に立つ.

Verilog シフトレジスタ 配列のギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

|  |  |

|  | |

|  | |

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  |  |

|  | |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

|  | |

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

| ||

|  |  |

|  |  |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

| ||

| ||

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

| ||

| ||

|  |  |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  | |

| ||

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  |  |

|  | |

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

parameter Verilog/SystemVerilogでは以下のようにparameterを設定することができる。parameterを使用することでモジュールの拡張性やコードの可読性が高くなる。 parameterの書式 parameter パラメータ名 = 値; verilogで二次元配列なんて書くことないと思ってたんだけどレジスタとか書くときに二次元配列すると楽なんですね。 `define BIT 32 `define ADDR 64 reg 0`BIT1 register 0`ADDR1;

Incoming Term: verilog シフトレジスタ 配列,

0 件のコメント:

コメントを投稿